|

市場調査レポート

商品コード

1911415

2.5Dおよび3D半導体パッケージング:市場シェア分析、業界動向と統計、成長予測(2026年~2031年)2.5D And 3D Semiconductor Packaging - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031) |

||||||

カスタマイズ可能

適宜更新あり

|

|||||||

| 2.5Dおよび3D半導体パッケージング:市場シェア分析、業界動向と統計、成長予測(2026年~2031年) |

|

出版日: 2026年01月12日

発行: Mordor Intelligence

ページ情報: 英文 120 Pages

納期: 2~3営業日

|

概要

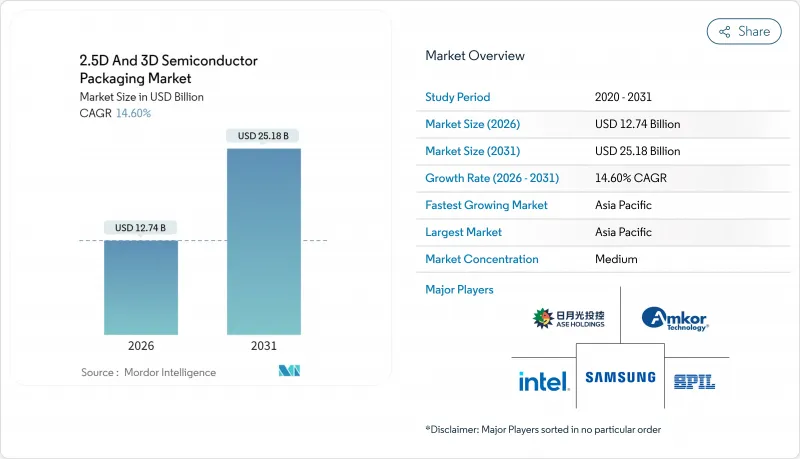

2.5Dおよび3D半導体パッケージング市場は、2025年の111億2,000万米ドルから2026年には127億4,000万米ドルへ成長し、2026年から2031年にかけてCAGR 14.6%で推移し、2031年までに251億8,000万米ドルに達すると予測されています。

テラバイト毎秒の帯域幅を必要とするAIトレーニングクラスター、自動車用センサーフュージョンプラットフォーム、スペース制約のあるモバイルデバイスに牽引され、エコシステムはインターポーザーの生産能力、チップレット規格、熱効率の高い基板への投資を進め、需要に追いつこうとしています。ファウンダリは利益率とロードマップの管理を確保するためパッケージングを自社内製化し、OSAT(受託組立テスト)企業は自動車およびフォトニクス使用事例向けの特殊組立に注力しています。米国、欧州、アジアにおける政府補助金は地域分散化を支援していますが、シリコンインターポーザーの不足と冷却限界が短期的な上昇余地を抑制しています。ガラスコア基板、ハイブリッドボンディング、コパッケージドオプティクスの普及が進む中、トランジスタ密度ではなくパッケージングの革新が、今後10年間のシステム性能を決定づけるでしょう。

世界の2.5Dおよび3D半導体パッケージング市場の動向と洞察

AI/MLワークロードが要求する超高メモリ帯域幅

1兆を超えるパラメータを有するハイパースケール学習モデルは従来のDDRインターフェースを飽和させ、GPUベンダーはソケットあたり3TB/sの帯域幅を実現するHBM3スタックとのロジック共封止を推進しています。シリコン貫通ビア(TSV)は配線長を短縮し遅延を低減、近接メモリ演算を可能にすることで、ディスクリート配置と比較しシステム電力消費を15%削減します。CoWoSおよびFoverosプラットフォームは、メモリとアクセラレータダイを共有インターポーザ上に配置します。このトポロジーは、フォームファクタの制約によりディスクリートDIMMが採用できないエッジ推論デバイスにも有益です。サムスンおよびSKハイニックスによるプロセッシング・イン・メモリのプロトタイプは、ロジックとストレージの境界をさらに曖昧にし、2.5Dおよび3D半導体パッケージング市場が性能ボトルネック解消の鍵となることを裏付けています。データセンター運営者は現在、ラックのエネルギー効率指標をパッケージ化されたメモリ帯域幅に直接結びつけており、パッケージングの決定がハイパースケール拡張のための資本支出の手段へと転換されています。

スマートフォンおよびウェアラブルの小型化

プレミアムスマートフォンは、システムインパッケージモジュール内に50以上の機能を統合し、基板面積を40%縮小。ファンアウトウエハーレベルパッケージングによりZ方向の高さを0.5mm未満に削減しています。スマートウォッチはさらに高密度化を追求し、100mm2未満のパッケージ内での無線機器、センサー、電源管理の異種統合を要求しています。次世代ウェアラブル向け伸縮性エレクトロニクスでは、有機基板では対応できない機械的歪みへの制約が生じ、反り防止機能を備えたRDLファースト・ファンアウトプロセスの採用が促進されています。ヒアラブルデバイスや医療用ウェアラブルの普及に伴い、生体適合性のある封止材や防湿バリアが必須となり、コンシューマーヘルス分野における2.5Dおよび3D半導体パッケージングの市場シェアが拡大しています。パッケージレベルのEMIシールドは、かつてはオプションでしたが、ポケットサイズのデバイス内でのミリ波通信や超広帯域測距には今や必須の要件となっています。

TSV/インターポーザ製造設備への設備投資拡大

CoWoS専用ラインのコストは標準組立ラインの3~4倍に達し、1拠点あたりの総投資額は100億米ドル規模に膨らみます。減価償却期間は10年に長期化し、OSATメーカーは価格競争力を損なう高固定費に縛られます。装置ベンダーの寡占化によりリードタイムは18ヶ月を超え、サプライチェーンリスクが高まっています。小規模な組立メーカーは、TSVエッチングモジュールやハイブリッドボンディングアライナーの資金調達ができず、ハイエンドの2.5Dおよび3D半導体パッケージング市場から撤退し、その力が上流のファウンダリに集中しています。

セグメント分析

3D TSVソリューションは2025年収益の43.72%を占め、14.85%のCAGRを維持することで、2.5Dおよび3D半導体パッケージング市場シェア競争の最前線に立っています。サムスンのHBM3Eスタックはデバイスあたり1.15TB/sの帯域幅を提供し、平面レイアウトと比較してフットプリントを60%縮小、基板の電源レールを30%削減します。

AI処理能力への需要が高まる中、マイクロバンプを排除し相互接続ピッチを10µm未満に縮小するハイブリッドボンディングが推進されています。TSMCのSoICサンプルでは相互接続密度が10倍向上し、高歩留まりでモノリシックレチクル性能にほぼ匹敵する結果を示しています。薄型化がTSVよりも優先される携帯電話分野ではファンアウトウエハーレベルパッケージングが依然重要であり、一方チップレットCPUではインターポーザベースの2.5Dブリッジが主流となっています。予測期間において、ガラスコアの採用と裏面給電TSV技術がカテゴリー間の境界を曖昧にし、混合モードパッケージが事実上のハイエンド構成として確立されることで、2.5Dおよび3D半導体パッケージング市場全体の規模が拡大する見込みです。

地域別分析

アジア太平洋地域は2025年の収益の60.05%を占め、台湾のCoWoSラインとマレーシアの世界バックエンド生産量における13%のシェアが牽引しました。2031年までの15.14%のCAGRは、基板およびテスト能力を増強するベトナムとタイの優遇措置に起因します。

北米はCHIPS法による補助金で加速:インテルのオハイオ複合施設とアムコールの20億米ドル規模アリゾナ工場が相まって、地域の処理能力を20%向上させます。防衛向けパッケージングの義務化により安全なワークロードが国内に集中し、SKハイニックスが計画するカンザス施設は主要クラウドデータセンター顧客に近い場所でHBM-ロジック組立を拡大します。

欧州は自動車・産業用信頼性分野に注力し、ドイツのシリコン・ザクセンやオランダのフォトニクス・クラスターが欧州地平線基金の支援を受けています。シェアはアジアに後れを取るもの、高信頼性分野におけるEUのコンテンツ比率が上昇し、地域の2.5D・3D半導体パッケージ市場規模を押し上げています。新興地域である南米、中東・アフリカでは、完全パッケージ済みデバイスを輸入しつつも、最終テストの現地化に向けた投資を誘致しており、これは世界的に集中したサプライチェーンのリスク分散が徐々に進んでいることを反映しています。

その他の特典:

- エクセル形式の市場予測(ME)シート

- アナリストによる3ヶ月間のサポート

よくあるご質問

目次

第1章 イントロダクション

- 調査の前提条件と市場の定義

- 調査範囲

第2章 調査手法

第3章 エグゼクティブサマリー

第4章 市場情勢

- 市場概要

- 市場促進要因

- AI/機械学習ワークロードが要求する超高メモリ帯域幅

- スマートフォンおよびウェアラブル機器の小型化

- 自動車向けADASの電動化推進

- ガラスコア基板の量産試験段階への移行

- 米国国防総省による国内3D-IC OSAT向けセキュアチップ義務化

- チップレット設計の急速な普及

- 市場抑制要因

- TSV/インターポーザ製造工場における設備投資の増加

- テスト設計の複雑さと歩留まり損失

- 世界におけるインターポーザー用シリコンインゴット不足問題

- 熱管理と信頼性の限界

- 業界バリューチェーン分析

- 規制情勢

- テクノロジーの展望

- ポーターのファイブフォース分析

- 供給企業の交渉力

- 買い手の交渉力

- 新規参入業者の脅威

- 代替品の脅威

- 競争企業間の敵対関係

第5章 市場規模と成長予測

- パッケージング技術別

- 2.5Dインターポーザ/FO-SoW

- 3D積層(TSV/ハイブリッドボンディング)

- ウエハーレベルCSP

- エンドユーザー産業別

- 民生用電子機器

- データセンターおよびHPC

- 通信およびテレコム

- 自動車およびADAS

- 医療機器

- 産業用およびIoT

- その他のエンドユーザー産業

- 用途別

- 高性能ロジック(CPU、GPU、AIアクセラレータ、ASIC、FPGA)

- メモリ(HBM、DRAMスタック、3D NAND)

- RFおよびフォトニクス

- 混合信号およびセンサー統合(ADC/DAC混合信号IC、MEMSセンサー、センサーハブパッケージ)

- 地域別

- 北米

- 米国

- カナダ

- メキシコ

- 欧州

- ドイツ

- フランス

- 英国

- イタリア

- その他欧州地域

- アジア太平洋地域

- 中国

- 日本

- 韓国

- インド

- その他アジア太平洋地域

- 南米

- ブラジル

- アルゼンチン

- その他南米

- 中東

- イスラエル

- サウジアラビア

- アラブ首長国連邦

- その他中東

- アフリカ

- 南アフリカ

- エジプト

- その他アフリカ

- 北米

第6章 競合情勢

- 市場集中度

- 戦略的動向

- ベンダーポジショニング分析

- 企業プロファイル

- Advanced Semiconductor Engineering Inc.

- Amkor Technology Inc.

- Taiwan Semiconductor Manufacturing Company Limited

- Samsung Electronics Co., Ltd.

- Intel Corporation

- Siliconware Precision Industries Co., Ltd.

- Powertech Technology Inc.

- Jiangsu Changjiang Electronics Technology Co., Ltd.

- GlobalFoundries Inc.

- United Microelectronics Corporation

- Tezzaron Semiconductor Corporation

- STATS ChipPAC Pte. Ltd.

- TongFu Microelectronics Co., Ltd.

- Hana Micron Inc.

- Kulicke and Soffa Industries Inc.